# Intel® 82578 GbE PHY

Datasheet

# **Product Features**

#### General

- 10 BASE-T IEEE 802.3 specification conformance

- 100 BASE-TX IEEE 802.3 specification conformance

- 1000 BASE-T IEEE 802.3 specification conformance

- IEEE 802.3u auto-negotiation conformance

- Supports carrier extension (half duplex)

- Loopback modes for diagnostics

- Advanced digital baseline wander correction

- Automatic MDI/MDIX crossover at all speeds of operation

- Automatic polarity correction

- MDC/MDIO management interface

- Flexible filters in PHY to reduce integrated LAN controller power

- Intel® VPro, Intel® Viiv and Virtualization support with appropriate Intel® chipset(s) components

- Smart speed operation for automatic speed reduction on faulty cable plants

- PMA loopback capable (no echo cancel)

- 802.1as/1588 conformance

- Intel® Stable Image Platform Program (SIPP)

- iSCSI Boot

## Performance

- Supports up to 4 KB jumbo frames (full duplex)<sup>1</sup>

- 802.10 and 802.1p

- Receive side Scaling (RSS)

- Two queues (Tx and Rx)

- Power

- Fully integrated linear regulation for 1.2 Vdc

- Reduced power consumption during normal operation and power down modes

- Integrated Intel® Auto Connect Battery Saver (ACBS)

- Single pin LAN Disable for easier BIOS implementation

- Low Power Link Up (LPLU)

- Media Access Controller (MAC)<sup>2</sup> /

- Physical Layer (PHY) Interconnect PCI-based interface for active state operation (S0 state)

- SMBus for host and management traffic (Sx low power state)

- Package / Design

- 48-pin package, 6 x 6 mm with a 0.4 mm lead pitch and an Exposed Pad\* for ground

- Three configurable LED outputs

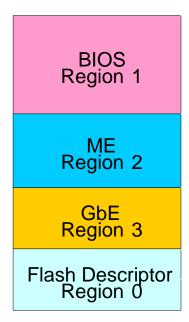

- Reduced Bill Of Material (BOM) cost by sharing SPI Flash with the Intel® 5 Series Express Chipset

Refer to the latest *Intel® 82578 Specification Update* for more details.

The MAC is incorporated into the Intel<sup>®</sup> 5 Series Express Chipset.

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or go to: http://www.intel.com/design/literature.htm.

Intel and Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries. \*Other names and brands may be claimed as the property of others.

Copyright © 2012, Intel Corporation. All Rights Reserved.

# Contents

| 1.0 | Intro  | duction1                                                          |

|-----|--------|-------------------------------------------------------------------|

|     | 1.1    | Scope1                                                            |

|     | 1.2    | Overview1                                                         |

|     | 1.3    | Main Flows                                                        |

|     | 1.4    | References                                                        |

|     | 1.5    | Product Codes                                                     |

|     | 1.6    | Product Matrix                                                    |

| 2.0 | Inter  | connects                                                          |

|     | 2.1    | Introduction5                                                     |

|     | 2.2    | PCIe-Based5                                                       |

|     |        | 2.2.1 PCIe Interface Signals                                      |

|     |        | 2.2.2 PCIe Operation and Channel Behavior                         |

|     | 2.3    | SMBus                                                             |

|     |        | 2.3.1 Overview                                                    |

|     | 2.4    | Transitions between SMBus and PCIe interfaces                     |

|     |        | 2.4.1 Switching from SMBus to PCIe                                |

|     |        | 2.4.2 Switching from PCIe to SMBus                                |

|     | 2.5    | Intel® 5 Series Express Chipset/82578 – SMBus/PCIe Interconnects9 |

| 3.0 | Pin I  | nterface                                                          |

|     | 3.1    | Pin Assignment                                                    |

|     |        | 3.1.1 Signal Type Definitions                                     |

|     |        | 3.1.2 PCIe Interface Pins (8)                                     |

|     |        | 3.1.3 SMBus Interface Pins (2)                                    |

|     |        | 3.1.4 Miscellaneous Pins (3)12                                    |

|     |        | 3.1.5 PHY Pins (14)                                               |

|     |        | 3.1.6 Testability Pins (5)                                        |

|     |        | 3.1.7 Power Pins (13)                                             |

|     |        | 3.1.8 LVR Power and Control Pins (3)14                            |

| 4.0 | Packa  | age15                                                             |

|     | 4.1    | Package Type and Mechanical                                       |

|     | 4.2    | Package Electrical and Thermal Characteristics                    |

|     | 4.3    | Power and Ground Requirements                                     |

|     | 4.4    | Pinouts (Top View, Pins Down)                                     |

|     | 4.5    | Ball Mapping19                                                    |

| 5.0 | Initia | lization                                                          |

| 5.0 | 5.1    | Power Up                                                          |

|     | 5.2    | Reset Operation                                                   |

|     | 5.3    | Timing Parameters                                                 |

|     | 5.5    | 5.3.1 Timing Requirements                                         |

|     |        | 5.3.2 Timing Guarantees                                           |

|     | _      | 5                                                                 |

| 6.0 |        | er Management and Delivery                                        |

|     | 6.1    | Power Targets                                                     |

|     | 6.2    | Power Delivery                                                    |

|     |        | 6.2.1 2.5 Vdc and 1.8 Vdc Supply                                  |

|     | 6.3    | 6.2.2 1.2 Vdc Supply                                              |

|     | 0.5    | 6.3.1 Global Power States                                         |

|     | 6.4    | Power Saving Features                                             |

|     | 0.7    | 6.4.1 Intel <sup>®</sup> Auto Connect Battery Saver (ACBS)        |

|     |        | 6.4.2 Automatic Link Downshift                                    |

| 7.0  | Devic      | e Functionality                                                    | 33 |

|------|------------|--------------------------------------------------------------------|----|

|      | 7.1        | Tx Flow                                                            | 33 |

|      | 7.2        | Rx Flow                                                            | 33 |

|      | 7.3        | Flow Control                                                       | 33 |

|      |            | 7.3.1 MAC Control Frames and Reception of Flow Control Packets     | 34 |

|      |            | 7.3.2 Transmitting PAUSE Frames                                    |    |

|      | 7.4        | Wake Up                                                            |    |

|      |            | 7.4.1 Host Wake Up                                                 |    |

|      |            | 7.4.2 Accessing The 82578's Wake Up Register Using MDIC            |    |

|      | 7.5        | PHY Loopback                                                       |    |

| 8.0  | Progr      | ammer's Visible State                                              |    |

| 0.0  | 8.1        | Terminology                                                        |    |

|      | 8.2        | MDIO Access                                                        |    |

|      | 8.3        | Addressing                                                         |    |

|      | 8.4        | Address Map                                                        |    |

|      | 8.5        | PHY Registers (Page 0)                                             |    |

|      | 0.5        |                                                                    |    |

|      | 0.0        |                                                                    |    |

|      | 8.6<br>8.7 | Port Control Registers (Page 769)                                  |    |

|      |            | Statistics Registers                                               |    |

|      | 8.8        | PCIe Registers                                                     |    |

|      | 8.9        | General Registers                                                  |    |

|      | 0 10       | 8.9.1 Interrupts                                                   |    |

|      | 8.10       | Wake Up Registers                                                  |    |

|      |            | 8.10.1 Accessing Wake Up Registers Using MDIC                      |    |

|      |            | 8.10.2 Host Wake Up Control Status Register Description            |    |

| 9.0  |            | Volatile Memory (NVM)                                              |    |

|      | 9.1        | Introduction                                                       | 87 |

|      | 9.2        | NVM Programming Procedure Overview                                 |    |

|      | 9.3        | LAN NVM Format and Contents                                        |    |

|      |            | 9.3.1 Hardware Accessed Words                                      |    |

|      |            | 9.3.2 Software Accessed Words                                      |    |

|      |            | 9.3.3 Basic Configuration Software Words1                          | 04 |

|      | 9.4        | Intel <sup>®</sup> 5 Series Express Chipset/82578 NVM Contents     | 06 |

| 10.0 | Intel      | $^{	extsf{B}}$ 5 Series Express Chipset MAC Programming Interface1 | 07 |

|      | 10.1       | Register Byte Ordering                                             |    |

|      | 10.2       | Register Conventions                                               |    |

|      |            | 10.2.1 PCI Configuration and Status Registers - CSR Space1         |    |

| 11.0 | Elect      | rical and Timing Specifications1                                   | 61 |

|      |            | Introduction 1                                                     |    |

|      | 11 2       | Operating Conditions                                               | 61 |

|      |            | 11.2.1 Absolute Maximum Ratings                                    |    |

|      |            | 11.2.2 Recommended Operating Conditions                            |    |

|      |            | 11.2.3 ESD Specifications                                          |    |

|      | 11 3       | Power Delivery                                                     |    |

|      | 11.5       | 11.3.1 Voltage Regulator Power Supply Specifications               |    |

|      |            | 11.3.2 Power On/Off Sequence                                       |    |

|      |            |                                                                    |    |

|      | 11.4  | I/O DC/AC Parameters                         | 165 |

|------|-------|----------------------------------------------|-----|

|      |       | 11.4.1 3.3 Vdc DC/IO                         | 165 |

|      |       | 11.4.2 2.5 Vdc/IO                            |     |

|      |       | 11.4.3 Input Buffer Only                     | 167 |

|      |       | 11.4.4 SMBus AC I/O                          | 168 |

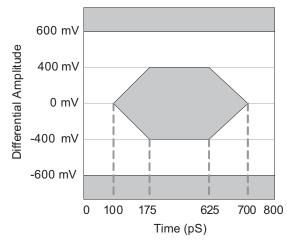

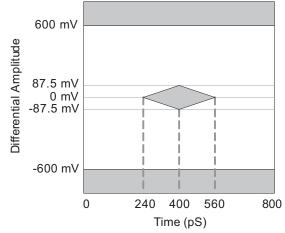

|      |       | 11.4.5 PCIe DC/AC Specifications             | 168 |

|      | 11.5  | Discrete/Integrated Magnetics Specifications | 171 |

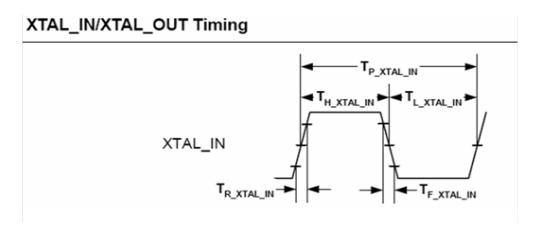

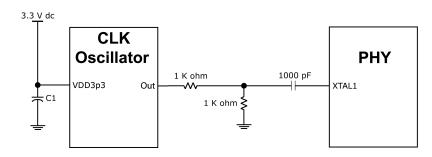

|      | 11.6  | Oscillator/Crystal Specifications            | 172 |

| 12.0 | Schei | matic and Board Layout Checklists            | 175 |

| 13.0 | Refer | ence Schematics                              | 177 |

| 14.0 | Mode  | ls                                           | 179 |

|      |       |                                              |     |

# **Revision History**

| Date          | Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| February 2012 | 2.5      | Revised Table 67 (bit 5 description).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| July 2011     | 2.4      | <ul> <li>Revised title page.</li> <li>Revised word 0x13 (new defaults for bits 7:6 and 15:9).</li> <li>Revised word 0x1B (new defaults for bits 1:0 and 4).</li> <li>Revised word 0x26 (new defaults for bits 10:9).</li> <li>Revised section 5.3.2 (Timing Guarantees, added T<sub>xtal</sub> and T<sub>por</sub> values).</li> <li>Revised section 11.4.2 (+3.3 Vdc level CMOS for signals JTAG_TCK, JTAG_TMS, and JTAG_TDI).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| June 2010     | 2.3      | <ul> <li>Update title page.</li> <li>Updated section 10.3.1.10 (bit 13 description).</li> <li>Added new values to section 12.4.2 (VIH).</li> <li>Removed old section 8.</li> <li>Updated section 10.3.1.11 (bit 12 and 13 desctiptions).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| February 2010 | 2.2      | <ul> <li>Updated figure 1.</li> <li>Updated table 2.</li> <li>Updated section 7.4 and 10.3.1.2 (added Intel® 5 Series Express Chipset references).</li> <li>Added power sequencing note to section 5.3.2.</li> <li>Updated section 6.4.2.2 (added Windows* 7 reference).</li> <li>Updated sections 7.4.1.3.1.4 through 7.4.1.3.1.7 and 7.4.1.3.2.1 through 7.4.1.3.2.2 (swapped Possible VLAN Tag and Possible Len/LLC/SNAP Header in the tables).</li> <li>Added a note to section 10.3.1.15 (LED behaviour).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                   |

| November 2009 | 2.1      | <ul> <li>Updated power consumption targets in section 6.</li> <li>Updated the NVM format and contents to match current NVM image.</li> <li>Added a PHY functionality section.</li> <li>Updated the recommended operating conditions in section 12.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| June 2009     | 2.0      | Initial Public Release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| May 2009      | 1.75     | Major revision (all sections).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| April 2009    | 1.0      | <ul> <li>Updated title page (advanced cable diagnostics).</li> <li>Added new Section "Intel® 5 Series Express Chipset/82578 - SMBus/PCIe Interconnects".</li> <li>Added SMBus specification reference to section 1.5.</li> <li>Updated pad size in section 4.1.</li> <li>Changed internal pin name from LAN_PWR_GOODn to LAN_DISABLE_N (all sections).</li> <li>Added new Section "Device Functionality".</li> <li>Added new Section "MAC Programming Interface".</li> <li>Added Appendix A, B, and C.</li> <li>Updated Section 11.6.</li> </ul>                                                                                                                                                                                                                                                                                                                                            |

| January 2009  | 0.98     | <ul> <li>Updated section 7.3.2 - removed power on/off sequence diagram.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| December 2008 | 0.97     | Updated tables 7 and 8 - added LAN disable estimated power numbers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| December 2008 | 0.96     | Updated tables 7 and 8 (latest power numbers).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Sept 2008     | 0.95     | <ul> <li>Section 2.2.2 (Removed last paragraph and Table 2).</li> <li>Section 2.3 (changed SMBCLK to SMB_CLK and SMBDATA to SMB_DATA).</li> <li>Section 2.3.1 (updated paragraph).</li> <li>Section 2.3.1.6 (Removed).</li> <li>Removed old sections 2.3.1.6.1, 2.3.1.6.2, and 2.3.1.7).</li> <li>Section 2.3.2.2.1 (updated table).</li> <li>Section 4.1 (added new mechanical drawing and pad size values).</li> <li>Section 5.3.2 (changed T<sub>XTAL</sub> parameter to 35 ms).</li> <li>Section 6.3.1.1 (updated paragraph).</li> <li>Section 6.3.1.2 (removed all mode 1 references and updated register references).</li> <li>Section 6.3.1 (added K1 Idle State information).</li> <li>Section 6.3.2 (changed KX to K0).</li> <li>Section 6.3.3 (updated register references).</li> <li>Section 6.4 (new section).</li> <li>Section 7.2.1 (added notes following table).</li> </ul> |

| Date       | Revision | Description                                                                                                                                                                                                                                                                                                                                                                         |

|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| July 2008  | 0.9      | <ul> <li>Added new section 8.0 "Non-Volatile Memory (NVM)".</li> <li>Added section 6.4 "Power Saving Features".</li> <li>Updated section 6.1 "Power Targets".</li> <li>Updated section 3.1.7 "Power Pins".</li> <li>Updated section 3.1.5.2 "Analog Pins".</li> </ul>                                                                                                               |

| May 2008   | 0.81     | • Updated pin description in Figure 3 and Section 4.5.                                                                                                                                                                                                                                                                                                                              |

| May 2008   | 0.8      | <ul> <li>Updated Tables 7 and 8 (added new power numbers).</li> <li>Updated Sections 3.1.7 and 3.1.8 (clarified power, LVR, and control pins).</li> <li>Updated Section 4.1 (Added Epad size specifications).</li> <li>Updated Figure 1 (removed ferrite beads from diagram).</li> <li>Updated Sections 1.2 (added note), 2.2 (added note), 2.3 (added note), and 7.2.2.</li> </ul> |

| April 2008 | 0.7      | Added a discrete/integrated magnetics specifications table to Section 7.0.                                                                                                                                                                                                                                                                                                          |

| Mar 2008   | 0.6      | Major revision (all sections).                                                                                                                                                                                                                                                                                                                                                      |

| Jan 2008   | 0.5      | Initial release (Intel Confidential).                                                                                                                                                                                                                                                                                                                                               |

# 1.0 Introduction

## 1.1 Scope

This document describes the external architecture for the 82578. It's intended to be a reference for software developers of device drivers, board designers, test engineers, or anyone else who might need specific technical or programming information about the 82578.

## 1.2 Overview

The 82578 is a single port Gigabit Ethernet Physical Layer Transceiver (PHY). It connects to the Intel<sup>®</sup> 5 Series Express Chipset integrated Media Access Controller (MAC) through a dedicated interconnect. The 82578 supports operation at 1000/100/ 10 Mb/s data rates. The PHY circuitry provides a standard IEEE 802.3 Ethernet interface for 1000BASE-T, 100BASE-TX, and 10BASE-T applications (802.3, 802.3u, and 802.3ab).

The 82578 is packaged in a small footprint QFN package. Package size is  $6 \times 6$  mm with a 0.4 mm lead pitch and a height of 0.85 mm, making it very attractive for small form-factor platforms.

The 82578 interfaces with its MAC through two interfaces: PCIe-based and SMBus. The PCIe (main) interface is used for all link speeds when the system is in an active state (S0) while the SMBus is used only when the system is in a low power state (Sx). In SMBus mode, the link speed is reduced to 10 Mb/s (dependent on low power options). The PCIe interface incorporates two aspects: a PCIe SerDes (electrically) and a custom logic protocol.

*Note:* The 82578 PCIe interface is not PCIe compliant. It operates at half of the PCI Express\* (PCIe\*) Specification v1.1 (2.5 GT/s) speed. In this datasheet the term PCIe-based is interchangeable with PCIe. There is no design layout differences between normal PCIe and the 82578's PCIe-based interface.

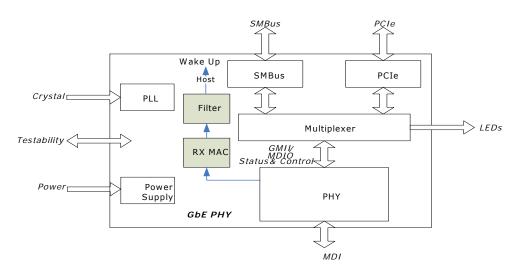

## Figure 1. 82578 Block Diagram

## 1.3 Main Flows

The 82578 main interfaces are PCIe and SMBus on the host side and the MDI interface on the link side. Transmit traffic is received from the MAC device through either PCIe or SMBus on the host interconnect and then transmitted on the MDI link. Receive traffic arrives on the MDI link and transferred to the MAC through either the PCIe or SMBus interconnects.

The MAC and system software control the 82578 functionality through two mechanisms:

- The 82578 configuration registers are mapped into the MDIO space and can be accessed by the MAC through the PCIe or SMBus interconnects.

- The MDIO traffic is embedded in specific fields in SMBus packets or carried by special packets over the PCIe encoded interconnect as defined by the custom protocol.

Specific flows are described in other sections of this document:

- Power delivery options are described in Section 4.3.

- Power management is described in Section 6.3.

# 1.4 References

- Information Technology Telecommunication & Information Exchange Between Systems - LAN/MAN - Specific Requirements - Part 3: Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and Physical Layer Specifications, IEEE Standard No.: 802.3-2002

- Intel® Ethernet Controllers Loopback Modes, Intel Corporation

- SMBus specification revision 2.0.

- Intel<sup>®</sup> 5 Series Express Chipset Family External Design Specification (Intel<sup>®</sup> 5 Series Express Chipset EDS), Intel Corporation

- Intel<sup>®</sup> 5 Series Express Chipset External Datasheet Specification, Intel Corporation

- Intel<sup>®</sup> 5 Series Express Chipset SPI Flash Programming Guide Application Note, Intel Corporation

- Intel<sup>®</sup> 82578 Schematic and Layout Checklists, Intel Corporation

- Intel<sup>®</sup> 82578 MDI Differential Trace and Power Loss Calculators, Intel Corporation

# 1.5 **Product Codes**

Table 1 lists the product ordering codes for the 82578 GbE controller. Refer to the  $Intel^{(R)}$  82578 GbE PHY Specification Update for device ordering information.

## Table 1. Product Ordering Codes

| Device  | Market Segment                    | Product Code |  |  |  |

|---------|-----------------------------------|--------------|--|--|--|

| 82578DM | Corporate desktop and workstation | WG82578DM    |  |  |  |

| 82578DC | Consumer desktop                  | WG82578DC    |  |  |  |

# 1.6 **Product Matrix**

|               |                                               |           |                        |           | Pe                      | erfor           | man                        | се                 | Ext                        | end                      | ed                      |                            |                       |                |             |          |            |              |

|---------------|-----------------------------------------------|-----------|------------------------|-----------|-------------------------|-----------------|----------------------------|--------------------|----------------------------|--------------------------|-------------------------|----------------------------|-----------------------|----------------|-------------|----------|------------|--------------|

| Method of     | Method of enabling/disabling features in SKUs |           |                        |           |                         | Driver          | MAC                        | MAC                | ЯΗΥ                        | Driver                   | ЪΗΥ                     | Driver                     | Driver                | Platform       | Platform    | BIOS     | BIOS       | FW           |

| Link<br>Speed | Platform                                      | Segment   | Description            | Device ID | Jumbo Frames (up to 4k) | 802.1Q & 802.1p | Receive Side Scaling (RSS) | 2 Tx & 2 Rx Queues | Low 'No-Link' Power (ACBS) | Link Speed Battery Saver | Low Power Linkup (LPLU) | Ability to Initiate a Team | Intel® Virtualization | Viiv (Home IT) | Intel® SIPP | PXE Boot | iSCSI Boot | Intel® vPro* |

| Gigabit       | Desktop                                       | Corporate | 82578 for<br>Corporate | 10EF      | x                       | х               | х                          | х                  | x                          |                          | х                       | х                          | x                     | x              | x           | x        | x          | х            |

| Cigabit       | Desktop                                       | Consumer  | 82578 for<br>Consumer  | 10F0      |                         | х               |                            |                    | х                          |                          | х                       | х                          |                       | х              |             | х        |            |              |

# 2.0 Interconnects

# 2.1 Introduction

The 82578 implements two interconnects to the MAC:

- PCIe A high-speed SerDes interface using PCIe electrical signaling at half speed while keeping the custom logical protocol for active state operation mode.

- System Management Bus (SMBus) A very low speed connection for low power state mode for manageability communication only. At this low power state mode the Ethernet link speed is reduced to 10 Mb/s.

## Table 2.82578 Interconnect Modes

| System                   | РНҮ      |            |  |  |  |  |

|--------------------------|----------|------------|--|--|--|--|

| System                   | SMBus    | PCIe       |  |  |  |  |

| S0 and PHY Power Down    | Not used | Idle       |  |  |  |  |

| S0 and Idle or Link Disc | Not used | Idle       |  |  |  |  |

| S0 and active            | Not used | Active     |  |  |  |  |

| Sx                       | Active   | Power down |  |  |  |  |

| Sx and DMoff             | Active   | Power down |  |  |  |  |

The 82578 automatically switches the in-band traffic between PCIe and SMBus based on the system power state.

## 2.2 PCIe-Based

*Note:* The 82578 PCIe interface is not PCIe compliant. It operates at half of the PCI Express\* (PCIe\*) Specification v1.1 (2.5 GT/s) speed. In this datasheet the term PCIe-based is interchangeable with PCIe. There is no design layout differences between normal PCIe and the 82578's PCIe-based interface. Standard PCIe validation tools cannot be used to validate this interface.

## 2.2.1 PCI e Interface Signals

The signals used to connect between the MAC and the PHY in this mode are:

- Serial differential pair running at 1.25 Gb/s for Rx

- Serial differential pair running at 1.25 Gb/s for Tx

- 100 MHz differential clock input to the PHY running at 100 MHz

- Power and clock good indication to the PHY PE\_RST\_N pin

- Clock control through CLK\_REQ\_N pin

# 2.2.2 PCI e Operation and Channel Behavior

The 82578 only runs at 1250 Mb/s speed, which is 1/2 of the PCIe Specification v1.1, 2.5 Gb/s PCIe frequency. Each of the PCIe root ports in the Intel<sup>®</sup> 5 Series Express Chipset-integrated MAC have the ability to operate with the 82578. The port configuration is pre-loaded from the NVM. The selected port adjusts the transmitter to run at the 1.25 GHz rate and does not need to be PCIe compliant.

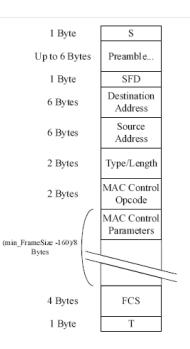

Packets transmitted and received over the PCIe interface are full Ethernet packets and not PCIe transaction/link/physical layer packets.

After the PCIe power-up sequence completes, each transmitter starts transmitting idle symbols and the receiver acquires synchronization as specified in 802.3z.

## 2.3 SMBus

*Note:* The 82578 SMBus must only be connected to SMLink0 in the Intel<sup>®</sup> 5 Series Express Chipset. No other device (like an external BMC) can be connected to SMLink0 when the 82578 is connected to the Intel<sup>®</sup> 5 Series Express Chipset SMLink0.

## 2.3.1 Overview

SMBus is used as an interface to pass traffic between the 82578 and the Intel<sup>®</sup> 5 Series Express Chipset when the system is in a low power state (Sx state). The interface is also used to enable the Intel<sup>®</sup> 5 Series Express Chipset to configure the 82578 as well as passing in-band information between them.

The SMBus uses two primary signals: SMB\_CLK and SMB\_DATA to communicate. Both of these signals float high with board-level pull-ups.

The SMBus specification has defined various types of message protocols composed of individual bytes. The message protocols supported by the 82578 are described in the relevant sections.

For more details about SMBus, see the SMBus specification.

## 2.3.1.1 SMBus Channel Behavior

The SMBus specification defines the maximum frequency of the SMBus as 100 KHz.

## 2.3.1.2 SMBus Addressing

The 82578's address is assigned using SMBus ARP protocol. The default SMBus address is 0xC8.

### 2.3.1.3 Bus Timeouts

The 82578 can detect (as a master or a slave) an SMB\_CLK timeout on the main SMBus. If the SMBus clock line is held low for 25 ms, the 82578 aborts the transaction.

As a slave, the 82578 detects the timeout and goes into an idle state. In idle, the slave releases the SMB\_CLK and SMB\_DATA lines. Any data that was received before the timeout might have been processed depending on the transaction.

As a master, the 82578 detects a timeout and issues a STOP on the SMBus at the next convenient opportunity and then brings the SMBus back to idle (releases SMB\_CLK and SMB\_DATA). Any master transaction that the 82578 detects a timeout on is aborted.

#### 2.3.1.4 Bus Hangs

Although uncommon, SMBus bus hangs can happen in a system. The reason for the hang is typically an unexpected, asynchronous reset or noise coupled onto the SMBus. Slaves can contribute to SMBus hangs by not implementing the SMBus timeouts as specified in SMBus 2.0 specification. Masters or host masters can contribute to SMBus hangs by not detecting the failures and by not attempting to correct the bus hangs.

Because of the potential bus hang scenario, the 82578 has the capability of detecting a hung bus. If SMB\_CLK or SMB\_DATA are stuck low for more than 35 ms, the 82578 forces the bus to idle (both SMB\_CLK and SMB\_DATA set) if it is the cause of the bus hang.

## 2.3.1.5 Packet Error Code (PEC) Support

PEC is defined in the SMBus 2.0 specification. It is an extra byte at the end of the SMBus transaction, which is a CRC-8 calculated on all of the preceding bytes (not including ACKs, NACKs, STARTs, or STOPs) in the SMBus transaction. The polynomial for this CRC-8 is:

$$x8 + x2 + x + 1$$

The PEC calculation is reset when any of the following occurs:

- A STOP condition is detected on the host SMBus

- An SMBus hang is detected on the host SMBus

- The SMB\_CLK is detected high for  ${\sim}50~\mu s$

## 2.3.1.6 SMBus ARP Functionality

The 82578 doesn't support ARP protocol.

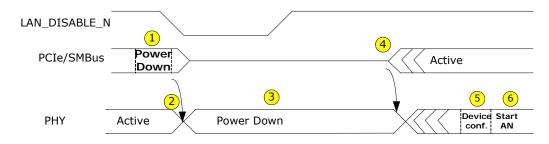

# 2.4 Transitions between SMBus and PCI e interfaces

## 2.4.1 Switching from SMBus to PCIe

Communication between the MAC and the 82578 is done through the SMBus each time the system is in a low power state (Sx);  $PE_RST_N$  signal is low. The MAC/PHY interface is needed to enable host wake up from the 82578.

Possible states for activity over the SMBus:

- 1. After power on (G3 to S5).

- 2. On system standby (Sx).

While in this state, the SMBus is used to transfer traffic, configuration, control and status between the MAC and the 82578.

The switching from the SMBus to PCIe is done when the PE\_RST\_N signal is high.

- Any transmit/receive packet that is not completed when PE\_RST\_N is asserted is discarded.

- Any in-band message that was sent over the SMBus and was not acknowledged is re-transmitted over PCIe.

## 2.4.2 Switching from PCIe to SMBus

The communication between the MAC and the 82578 is done through PCIe each time the system is in active power state (S0); PE\_RST\_N signal is high. Switching the communication to SMBus is only needed to enable host wake up in low power states and is controlled by the Intel® 5 Series Express Chipset.

The switching from PCIe to SMBus is done when the PE\_RST\_N signal is low.

- Any transmit/receive packet that is not completed when PE\_RST\_N goes to 0b is discarded.

- Any in-band message that was sent over PCIe and was not acknowledged is retransmitted over SMBus.

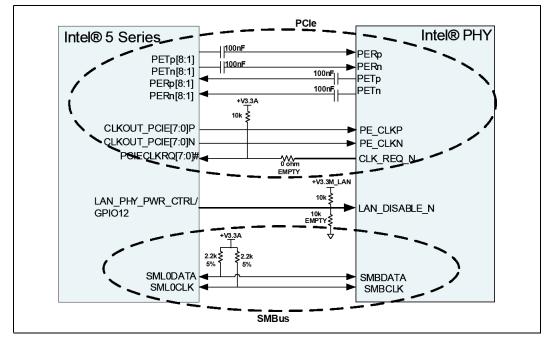

#### 2.5 Intel® 5 Series Express Chipset/82578 – SMBus/PCIe Interconnects

The 82578 can be connected to any x1 PCIe port in Intel<sup>®</sup> 5 Series Express Chipset. The PCIe port that connects to the 82578 is selected by PCHSTRP9, bits [11:8] in the SPI Flash descriptor region. For more information on this setting, please refer to the Intel<sup>®</sup> 5 Series Express Chipset External Datasheet Specification. The Intel<sup>®</sup> 5 Series Express Chipset-to-82578 PCIe port connection in the reference schematic must match the previously mentioned Intel<sup>®</sup> 5 Series Express Chipset SPI strap setting. Choosing another port can result in unexpected system behavior.

The SMBus/PCIe interface can be configured in as shown Figure 2.

#### Figure 2. Intel® 5 Series Express Chipset/82578 Interconnects

#### Notes:

- 1. Any free PCIe ports (ports 1-8) can be used to connect to the 82578 PCIe Interface.

- Any CLKOUT\_PCIE[7:0] and PCIECLKRQ[7:0] can be used to connect to PE\_CLK for the 82578.

PETp/n, PERp/n, PE\_CLKp/n should be routed as differential pair as per the PCIe specification.

*Note:* This page intentionally left blank.

# 3.0 Pin Interface

# 3.1 Pin Assignment

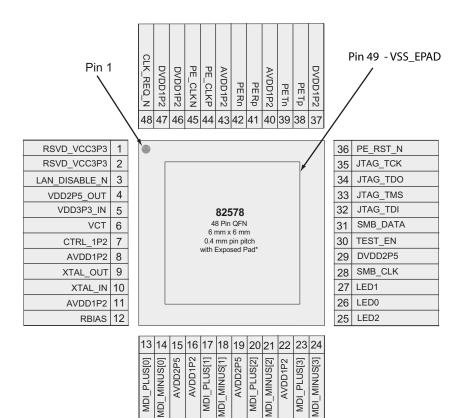

The 82578 is packaged in a 48-pin package,  $6 \times 6$  mm with a 0.4 mm lead pitch. There are 48 pins on the periphery and a die pad (Exposed Pad\*) for ground.

# 3.1.1 Signal Type Definitions

| Signal Type | Definition                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| In          | Input is a standard input-only signal.                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| I           | A standard input-only signal.                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Out (0)     | Fotem pole output is a standard active driver.                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| T/s         | Tri-state is a bi-directional, tri-state input/output pin.                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| S/t/s       | Sustained tri-state is an active low tri-state signal owned and driven by one and only one agent at a time. The agent that drives an s/t/s pin low must drive it high for at least one clock before letting it float. A new agent cannot start driving an s/t/s signal any sooner than one clock after the previous owner tri-states it. |  |  |  |  |  |  |

| O/d         | Open drain enables multiple devices to share as a wire-OR.                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| Analog      | Analog input/output signal.                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| A-in        | Analog input signal.                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| A-out       | Analog output signal.                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| В           | Input bias                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

*Note:* Refer to the reference schematics for pin connection details. Contact your Intel representative for access.

# 3.1.2 PCIe Interface Pins (8)

| Pin Name           | Pin #    | Туре  | Op Mode | Name and Function                                                          |

|--------------------|----------|-------|---------|----------------------------------------------------------------------------|

| PE_RST_N           | 36       | Ι     | Input   | PCIe reset.                                                                |

| PETp<br>PETn       | 38<br>39 | A-out | Output  | PCIe Tx.                                                                   |

| PERp<br>PERn       | 41<br>42 | A-in  | Input   | PCIe Rx.                                                                   |

| PE_CLKP<br>PE_CLKN | 44<br>45 | A-in  | Input   | PCIe clock.                                                                |

| CLK_REQ_N          | 48       | O/d   | Output  | Clock request. Connect to VCC3P3 through a 10 K $\Omega$ pull-up resistor. |

# 3.1.3 SMBus Interface Pins (2)

| Pin Name | Pin # | Туре | Op Mode | Name and Function                                                                                                                  |

|----------|-------|------|---------|------------------------------------------------------------------------------------------------------------------------------------|

| SMB_CLK  | 28    | O/d  | BI-dir  | SMBus clock. Pull this signal up to 3.3 Vdc (auxiliary supply <sup>1</sup> ) through a 2.2 K $\Omega$ resistor (while in Sx mode). |

| SMB_DATA | 31    | O/d  | BI-dir  | SMBus data. Pull this signal up to 3.3 Vdc (auxiliary supply) through a 2.2 K $\Omega$ resistor (while in Sx mode).                |

1. AUX power means the power rail is available in all power states including G3 to S5 transitions and Sx states with Wake on LAN (WoL) enabled.

# 3.1.4 Miscellaneous Pins (3)

| Pin Name      | Pin # | Туре | Op Mode | Name and Function                                         |

|---------------|-------|------|---------|-----------------------------------------------------------|

| RSVD1_VCC3P3  | 1     | T/s  |         | Connect to VCC3P3 through a 5%, 3.01 K $\Omega$ resistor. |

| RSVD2_VCC3P3  | 2     | T/s  |         | Connect to VCC3P3 through a 5%, 3.01 K $\Omega$ resistor. |

| LAN_DISABLE_N | 3     | Ι    |         | Note: When this pin is set to 0b, the 82578 is disabled.  |

# 3.1.5 PHY Pins (14)

# 3.1.5.1 LEDs (3)

This table lists the functionality of the LED output pins. Refer to the  $Intel^{(R)}$  5 Series Family Platform Design Guide (PDG) for LED connection details.

| Pin Name | Pin # | Туре | Op Mode | Name and Function                                                  |

|----------|-------|------|---------|--------------------------------------------------------------------|

| LED0     | 26    | 0    | Output  | This signal is used for the programmable LED (LINK_LINK/ACTIVITY). |

| LED1     | 27    | 0    | Output  | This signal is used for the programmable LED (LINK_1000).          |

| LED2     | 25    | 0    | Output  | This signal is used for the programmable LED (LINK_100).           |

# 3.1.5.2 Analog Pins (11)

| Pin Name                                                   | Pin#                 | Туре   | Op Mode | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|------------------------------------------------------------|----------------------|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MDI_PLUS[0]<br>MDI_MINUS[0]                                | 13<br>14             | Analog | Bi-dir  | <ul> <li>Media Dependent Interface[0]</li> <li><b>1000BASE-T:</b> In MDI configuration, MDI[0]+/- corresponds to BI_DA+/- and in MDI-X configuration MDI[0]+/- corresponds to BI_DB+/</li> <li><b>100BASE-TX:</b> In MDI configuration, MDI[0]+/- is used for the transmit pair and in MDI-X configuration MDI[0]+/- is used for the receive pair.</li> <li><b>10BASE-T:</b> In MDI configuration, MDI[0]+/- is used for the transmit pair and in MDI-X configuration MDI[0]+/- is used for the receive pair.</li> </ul> |  |

| MDI_PLUS[1]<br>MDI_MINUS[1]                                | 17<br>18             | Analog | Bi-dir  | Media Dependent Interface[1]<br><b>1000BASE-T:</b> In MDI configuration, MDI[1]+/- corresponds to<br>BI_DB+/- and in MDI-X configuration MDI[1]+/- corresponds to<br>BI_DA+/<br><b>100BASE-TX:</b> In MDI configuration, MDI[1]+/- is used for the<br>receive pair and in MDI-X configuration MDI[1]+/- is used for the<br>transmit pair.<br><b>10BASE-T:</b> In MDI configuration, MDI[1]+/- is used for the<br>receive pair and in MDI-X configuration MDI[1]+/- is used for the<br>transmit pair.                     |  |

| MDI_PLUS[2]<br>MDI_MINUS[2]<br>MDI_PLUS[3]<br>MDI_MINUS[3] | 20<br>21<br>23<br>24 | Analog | Bi-dir  | Media Dependent Interface[3:2]<br><b>1000BASE-T:</b> In MDI configuration, MDI[3:2]+/- corresponds to<br>BI_DA+/- and in MDI-X configuration MDI[3:2]+/- corresponds to<br>BI_DB+/<br><b>100BASE-TX:</b> Unused.<br><b>10BASE-T:</b> Unused.                                                                                                                                                                                                                                                                             |  |

| XTAL_OUT                                                   | 9                    | 0      |         | Output crystal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| XTAL_IN                                                    | 10                   | Ι      |         | Input crystal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| RBIAS                                                      | 12                   | Analog |         | Connect to ground through a 2.37 K $\Omega$ +/-1%.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

# 3.1.6 Testability Pins (5)

| Pin Name | Pin # | Туре     | Op Mode | Name and Function                                                                                                     |

|----------|-------|----------|---------|-----------------------------------------------------------------------------------------------------------------------|

| JTAG_TCK | 35    | In       | Input   | JTAG clock input.                                                                                                     |

| JTAG_TDI | 32    | In<br>PU | Input   | JTAG TDI input.                                                                                                       |

| JTAG_TDO | 34    | T/s      | Output  | JTAG TDO output.                                                                                                      |

| JTAG_TMS | 33    | In<br>PU | Input   | JTAG TMS input.                                                                                                       |

| TEST_EN  | 30    | In       | Input   | Should be connected to ground through a 1 K $\!\Omega$ resistor, when connected to logic 1b and test mode is enabled. |

*Note:* The 82578 uses the JTAG interface to support XOR files for manufacturing test. BSDL is not supported.

# 3.1.7 **Power Pins (13)**

| Pin Name   | Pin #                    | Туре  | Name and Function                                                  |

|------------|--------------------------|-------|--------------------------------------------------------------------|

| AVDD1P2    | 8, 11, 16, 22,<br>40, 43 | Power | 1.2 Vdc supply.                                                    |

| AVDD1P2    | 8                        | Power | 1.2 Vdc sense feedback.                                            |

| AVDD2P5    | 15, 19                   | Power | 2.5 Vdc supply.                                                    |

| DVDD1P2    | 37, 46, 47               | Power | 1.2 Vdc supply; connected to DVDD using 0 $\Omega$ 0805 resistors. |

| DVDD2P5    | 29                       | Power | 2.5 Vdc supply to I/O.                                             |

| VDD3P3_IN  | 5                        | Power | 3.3 Vdc supply.                                                    |

| VDD2P5_OUT | 4                        | Power | 2.5 Vdc out.                                                       |

# 3.1.8 LVR Power and Control Pins (3)

| Pin Name | Pin # | Туре   | Name and Function                                                                        |

|----------|-------|--------|------------------------------------------------------------------------------------------|

| CTRL1P2  | 7     | Analog | Connect to the base of the PNP.                                                          |

| VCT      | 6     | Analog | Regulator output; connect to 1.8 Vdc supply and a center tap, 1 $\mu\text{F}$ capacitor. |

# 4.0 Package

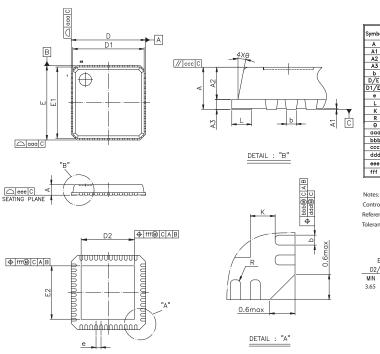

# 4.1 Package Type and Mechanical

The 82578 is a 6 mm x 6 mm, 48-pin QFN Halogen Free, Pb Free package with a pad size of 3.80 mm x 3.80 mm.

|        | Dime  | nsion i  | n mm | Dime      | nsion ir | inch  |

|--------|-------|----------|------|-----------|----------|-------|

| Symbol | MIN   | NOM      | MAX  | MIN       | NOM      | MAX   |

| Α      | 0.80  | 0.85     | 0.90 | 0.031     | 0.033    | 0.035 |

| A1     | 0.00  | 0.02     | 0.05 | 0.000     | 0.001    | 0.002 |

| A2     | 0.60  | 0.65     | 0.70 | 0.024     | 0.026    | 0.028 |

| A3     |       | 0.20 RE  | F    |           | 0.008 RE |       |

| b      | 0.15  | 0.20     | 0.25 | 0.006     | 0.008    | 0.010 |

| D/E    |       | 6.00 BSC |      |           | 0.236 BS | с     |

| D1/E1  |       | 5.75 BSC | ;    | 0.226 BSC |          |       |

| е      |       | 0.40 BSC | ;    | 0.016 BSC |          |       |

| L      | 0.30  | 0.40     | 0.50 | 0.012     | 0.016    | 0.020 |

| к      | 0.20  |          |      | 0.008     |          |       |

| R      | 0.075 |          |      | 0.003     |          |       |

| θ      | 0°    |          | 14   | 0.        |          | 14"   |

| aaa    |       |          | 0.10 |           |          | 0.004 |

| bbb    |       |          | 0.07 |           |          | 0.003 |

| ccc    |       |          | 0.10 |           |          | 0.004 |

| ddd    |       |          | 0.05 |           |          | 0.002 |

| eee    |       |          | 0.08 |           |          | 0.003 |

| fff    |       |          | 0.10 |           |          | 0.004 |

Notes: Controlling Dimension - Millimeter Reference Document - JEDEC MO-220 Tolerance Requirement for D1/E1: +/- 0.1 mm

Exposed

Pad

Size

D2/E2

(mm)

D2/E2

(inch)

MIN

NOM

MAX

MIN

NOM

MAX

3.65

3.80

3.95

0.144

0.150

0.156

# Figure 3. Package Dimensions

# 4.2 Package Electrical and Thermal Characteristics

The thermal resistance from junction to case, qJC, is  $15.1 \times C/Watt$ .

The thermal resistance from junction to ambient, qJA, is as follows: 4-layer PCB, 85 degrees ambient.

| Air Flow (m/s) | Maximum T <sub>J</sub> | qJA (×C/Watt) |

|----------------|------------------------|---------------|

| 0              | 119                    | 34            |

| 1              | 118                    | 33            |

| 2              | 116                    | 31            |

No heat sink is required.

# 4.3 **Power and Ground Requirements**

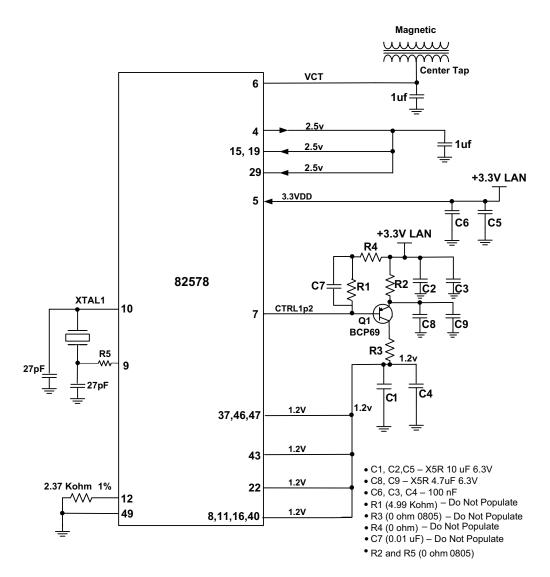

The 82578 requires three power supplies plus one internal power rail that is brought out for decoupling. Figure 4 shows a typical power delivery configuration that can be implemented.

*Note:* Power delivery can be customized based on a specific OEM platform configuration.

Figure 4. 82578 Power Delivery Diagram

# 4.4 Pinouts (Top View, Pins Down)

Figure 5. 82578 Pinouts

# 4.5 Ball Mapping

| Pin Name      | Side  | Pin Number | Pin Name     | Side   | Pin Number |

|---------------|-------|------------|--------------|--------|------------|

| RSVD_VCC3P3   | Left  | 1          | MDI_PLUS[0]  | Bottom | 13         |

| RSVD_VCC3P3   | Left  | 2          | MDI_MINUS[0] | Bottom | 14         |

| LAN_DISABLE_N | Left  | 3          | AVDD2P5      | Bottom | 15         |

| VDD2P5_OUT    | Left  | 4          | AVDD1P2      | Bottom | 16         |

| VDD3P3_IN     | Left  | 5          | MDI_PLUS[1]  | Bottom | 17         |

| VCT           | Left  | 6          | MDI_MINUS[1] | Bottom | 18         |

| CTRL1P2       | Left  | 7          | AVDD2P5      | Bottom | 19         |

| AVDD1P2       | Left  | 8          | MDI_PLUS[2]  | Bottom | 20         |

| XTAL_OUT      | Left  | 9          | MDI_MINUS[2] | Bottom | 21         |

| XTAL_IN       | Left  | 10         | AVDD1P2      | Bottom | 22         |

| AVDD1P2       | Left  | 11         | MDI_PLUS[3]  | Bottom | 23         |

| RBIAS         | Left  | 12         | MDI_MINUS[3] | Bottom | 24         |

| LED2          | Right | 25         | DVDD1P2      | Тор    | 37         |

| LED0          | Right | 26         | РЕТр         | Тор    | 38         |

| LED1          | Right | 27         | PETn         | Тор    | 39         |

| SMB_CLK       | Right | 28         | AVDD1P2      | Тор    | 40         |

| DVDD2P5       | Right | 29         | PERp         | Тор    | 41         |

| TEST_EN       | Right | 30         | PERn         | Тор    | 42         |

| SMB_DATA      | Right | 31         | AVDD1P2      | Тор    | 43         |

| JTAG_TDI      | Right | 32         | PE_CLKP      | Тор    | 44         |

| JTAG_TMS      | Right | 33         | PE_CLKN      | Тор    | 45         |

| JTAG_TDO      | Right | 34         | DVDD1P2      | Тор    | 46         |

| JTAG_TCK      | Right | 35         | DVDD1P2      | Тор    | 47         |

| PE_RST_N      | Right | 36         | CLK_REQ_N    | Тор    | 48         |

| VSS_EPAD      | EPAD  | 49         |              |        |            |

*Note:* This page intentionally left blank.

# 5.0 Initialization

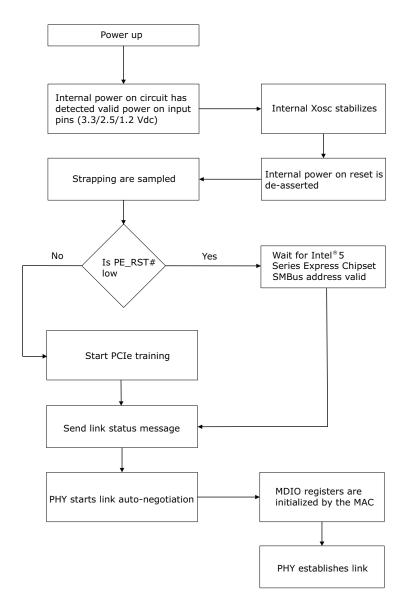

# 5.1 Power Up

| Note |                                                                                                 |

|------|-------------------------------------------------------------------------------------------------|

| 1    | Platform power ramps up (3.3 V dc/2.5/1.2 Vdc)                                                  |

| 2    | XTAL is stable after T <sub>XTAL</sub> sec.                                                     |

| 3    | Internal Power On Reset triggers $T_{POR}$ after XTAL is stable. Strapping options are latched. |

| 4    | PCIe training if PE reset is de-asserted.                                                       |

| 5    | Wait for Intel <sup>®</sup> 5 Series Express Chipset SMBus address valid.                       |

| 6    | Send Link Status message.                                                                       |

| 7    | MAC configures the 82578.                                                                       |

| 8    | PHY goes through auto-negotiation to acquire link.                                              |

#### **Reset Operation** 5.2

The reset sources for the 82578 are as follows:

- Internal Power On Reset (POR) The 82578 has an internal mechanism for sensing the power pins. Until power is up and stable, the 82578 generates an internal active low reset. This reset acts as a master reset for the 82578. While the internal reset is 0b, all registers in the 82578 are reset to their default values. Strapping values are latched after Internal POR is de-asserted.

- PHY Soft Reset A PHY reset caused by writing to bit 15 in MDIO register 0. Setting the bit resets the PHY, but does not reset non-PHY parts. Soft reset is used mainly to program the PHY to a different work point without affecting functionality of the rest of the device. Once the PHY completes its internal reset, a reset complete indication is sent to the MAC over the interconnect. The MAC then configures the PHY.

Note:

The MAC configures the PHY registers. Other the 82578 registers do not need to be configured.

- PCIe Reset After asserting a PCIe reset, the 82578 stops the PCIe interface and if in the middle of transmitting a packet it will be dropped. De-asserting PCIe reset resets the internal FIFO unless wake-up is activated and causes a switch from SMBus to PCIe.

- In-Band Reset An in-band message causing complete reset of the 82578 except the wake up filters content.

The effect of the various reset options on these and other registers is listed in Table 4.

Table 4 lists the impact of each the 82578 reset.

#### 82578 Resets Table 4.

| Effects/<br>Sources            | PCIe<br>Interface | Non-PHY<br>Registers<br>and State | PHY<br>Registers<br>and State | Reset<br>Complete<br>Indication | Strapping<br>Options | Fuse<br>Registers | Move Out<br>of Power<br>Down<br>Mode | Wake Up<br>Register |

|--------------------------------|-------------------|-----------------------------------|-------------------------------|---------------------------------|----------------------|-------------------|--------------------------------------|---------------------|

| Internal<br>POR <sup>1</sup>   | $\checkmark$      | $\checkmark$                      | $\checkmark$                  | $\checkmark$                    | $\checkmark$         | $\checkmark$      |                                      | $\checkmark$        |

| PHY Soft<br>Reset <sup>2</sup> |                   |                                   | $\checkmark$                  | $\checkmark$                    |                      |                   |                                      |                     |

| PCIe Reset                     | $\checkmark$      |                                   |                               |                                 |                      |                   |                                      |                     |

| In-Band<br>Reset               | $\checkmark$      | $\checkmark$                      | $\checkmark$                  | $\checkmark$                    |                      | $\checkmark$      | $\checkmark$                         |                     |

1. Asserting a 3.3 Vdc power on reset should move the PHY out of power down mode.

PHY registers (page 0 in MDIO space and any aliases to page 0) are reset during a PHY soft reset. The rest of the 82578's MDIO space is not reset. 2.

# 5.3 Timing Parameters

# 5.3.1 Timing Requirements

The 82578 requires the following start-up and power-state transitions.

## Table 5.Timing Requirements

| Parameter           | Description                                                           | Min. | Max.  | Notes |

|---------------------|-----------------------------------------------------------------------|------|-------|-------|

| T <sub>r2init</sub> | Completing a PHY configuration following a reset complete indication. |      | 0.5 s |       |

## 5.3.2 Timing Guarantees

The 82578 guarantees the following start-up and power state transition related timing parameters.

*Note:* For platform power sequencing requirements for the Intel® 5 Series Express Chipset MAC, refer to the Intel® 5 Series Express Chipset EDS.

## Table 6.Timing Guarantees

| Parameter              | Description                                                    | Min   | Мах   | Notes                                                               |

|------------------------|----------------------------------------------------------------|-------|-------|---------------------------------------------------------------------|

| T <sub>PHY_Reset</sub> | Reset de-assertion to PHY reset complete                       |       | 10 ms | PHY configuration should be delayed until PHY completes it's reset. |

| T <sub>c2an</sub>      | Cable connect at start of auto-negotiation                     | 1.2 s | 1.3 s | Per 802.3 specification.                                            |

| T <sub>xtal</sub>      | X <sub>tal</sub> frequency stable after platform power ramp up |       | 45 ms |                                                                     |

| T <sub>por</sub>       | Internal POR trigger after<br>X <sub>tal</sub> stable          |       | 40 ms |                                                                     |

#### **Power Management and Delivery** 6.0

This section describes how power management is implemented in the 82578.

#### **Power Targets** 6.1

Table 7 lists the targets for device power for the 82578. Note that power is reduced according to link speed and link activity.

Note: Device power is the power dissipated by the 82578.

#### 82578 Power Consumption Targets – External 1.8 Vdc<sup>1</sup> Table 7.

| System State |                                 | Link State                      | 3.3 Vdc<br>Current<br>[mA] | 1.8 Vdc<br>Current<br>[mA] | 1.2 Vdc<br>Current<br>[mA] | Device<br>Power<br>[mW] | Solution<br>Power<br>(mW)<br>BCP69<br>Solution |

|--------------|---------------------------------|---------------------------------|----------------------------|----------------------------|----------------------------|-------------------------|------------------------------------------------|

| S0 Maximum   |                                 | 1000Mb – active @<br>90 °C [Ta] | 22                         | 193                        | 284                        | 761                     | 1647                                           |

| S0 Typical   |                                 | 1000 Mb/s active                | 22                         | 193                        | 282                        | 758                     | 1640                                           |

|              |                                 | 100 Mb/s active                 | 14                         | 43                         | 121                        | 259                     | 587                                            |

|              |                                 | 10 Mb/s active                  | 15                         | 114                        | 72                         | 341                     | 663                                            |

|              |                                 | 1000 Mb/s idle                  | 22                         | 194                        | 237                        | 706                     | 1495                                           |

|              |                                 | 100 Mb/s idle                   | 13                         | 42                         | 71                         | 204                     | 416                                            |

|              |                                 | 10 Mb/s idle                    | 11                         | 1                          | 25                         | 68                      | 122                                            |

|              |                                 | Cable disconnect                | 9                          | 0                          | 10                         | 42                      | 63                                             |

|              |                                 | LAN disable                     | 9                          | 0                          | 14                         | 47                      | 76                                             |

| Sx           | Wake on<br>LAN (WoL)<br>enabled | 100 Mb/s - WoL                  | 13                         | 42                         | 68                         | 200                     | 406                                            |

|              |                                 | 10 Mb/s - WoL                   | 11                         | 1                          | 23                         | 66                      | 116                                            |

|              | WoL<br>disabled                 | Disabled in BIOS <sup>2</sup>   | 0                          | 0                          | 0                          | 0                       | 0                                              |

|              |                                 | Disabled in driver              | 9                          | 0                          | 14                         | 47                      | 76                                             |

Measured power could be higher or lower based on measurement setup and PHY power delivery configuration.

Assumes the system is in the Moff state and SLP\_LAN# is used to gate PHY power.

The following sections describe requirements in specific power states.

# 6.2 **Power Delivery**

The 82578 operates from a 3.3 Vdc external power rail (see Figure 7).

## 6.2.1 2.5 Vdc and 1.8 Vdc Supply

The 2.5 Vdc and 1.8 Vdc are is supplied by internal LVRs as shown in the schematics that follow.

## 6.2.2 **1.2 Vdc Supply**

The 1.2 Vdc rail can be supplied in one of two ways (see Figure 4):

- An external power supply not dependent on support from the 82578. For example, the platform designer might choose to route a platform-available 1.2 Vdc supply to the 82578. Intel<sup>®</sup> 5 Series Express Chipset

- A discrete LVR solution, where the base current of PNP power transistor is driven by the 82578, while the power transistor is placed externally.

# 6.3 Power Management

## 6.3.1 Global Power States